Exploring a MIPS CPU that isn't RISC and even uses variable length instructions: https://www.eejournal.com/article/mips-i7200-breaks-the-chain/

(In embedded markets it's a lot easier to sell a new ISA apparently!)

miniblog.

Related Posts

After seeing yet another YAML dialect for controlling systems, I think we need a hierarchy of YAML dialect expressiveness.

(1) Has its own variable binding system.

(2) Supports if statements.

(3) Supports loops.

(4) Supports function definition.

2 seems to be the most common, but I've seen all of 1-3. Does level 4 exist in the wild yet?

After seeing yet another YAML dialect for controlling systems, I think we need a hierarchy of YAML dialect expressiveness.

(1) Has its own variable binding system.

(2) Supports if statements.

(3) Supports loops.

(4) Supports function definition.

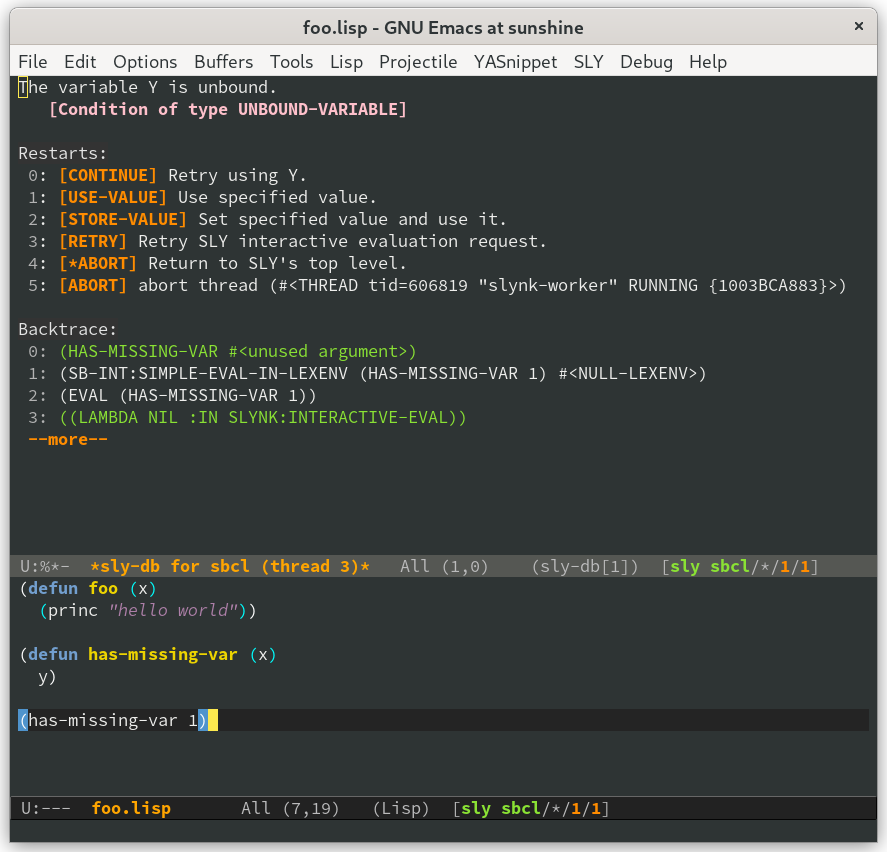

I'm impressed by how many options I'm offered in Common Lisp (in this case sbcl on Sly) for a simple error like an invalid variable name!